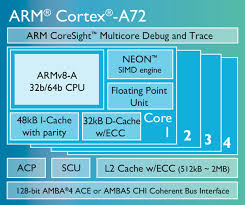

ARM的Cortex-A72是一个微架构实施ARMv8-A的64位指令集设计由ARM控股。Cortex-A72是一个无序的 超标量流水线。[1]它可以作为SIP核心到授权,并且其设计使得它适合与其他SIP核心的集成(例如GPU,显示控制器,DSP,图像处理器等)转换成一个模构成片上系统(SOC )。

概述

-

流水线处理器出现严重故障,推测问题 3路超标量执行管道

-

DSP和NEON SIMD扩展是每个核心的强制性

-

VFPv4板上浮点单元(每个内核)

-

硬件虚拟化支持

-

Thumb-2指令集编码减少了32位程序的大小,对性能几乎没有影响。

-

TrustZone安全扩展

-

程序跟踪宏单元和CoreSight设计套件,用于不显眼的跟踪指令执行

-

32 KiB数据(2路组相关)+ 48 KiB指令(3路组相关)每个核心的L1缓存

-

集成的低延迟2级(16路组相关)高速缓存控制器,每个集群512 KB到4 MB可配置的大小

-

48条目全关联L1指令翻译后备缓冲器(TLB),支持4 KiB,64 KiB和1 MB页面大小

-

32条目全关联L1数据翻译后备缓冲器(TLB),支持4 KiB,64 KiB和1 MB页面大小

-

4路组关联,每个核心1024条统一L2 TLB,支持命中未命中

-

复杂的分支预测算法,显着提高性能,减少误预测和猜测的能量

-

早期IC标签-3路L1缓存直接映射电源*

-

区域化TLB和μBTB标记

-

小偏移分支目标优化

-

抑制多余的分支预测器访问